# **Inductance Extraction**

Milivoj Kovač and Adrijan Barić Faculty of Electrical Engineering and Computing, University of Zagreb, Unska 3, 10000 Zagreb, E-mail: adrijan.baric@fer.hr

Abstract – Implementation of the algorithm for on-chip inductance extraction based on the return-limited inductance method is presented. Numerical problems with matrix calculations are presented and a solution is provided. The results of the analysis for various lengths and distances between lines are given.

### I. INTRODUCTION

Recently inductance and inductive coupling have become important in the timing and noise analysis of a growing number of on-chip signal lines. That is why inductance must be included to accurately predict rise and fall times and delays in timing analysis [1-4]. Extraction of on-chip inductances has become as important as the extraction of parasitic on-chip resistances and capacitances due to continuing increase of clock frequencies.

There are several approaches for inductance calculation. Traditionally, the concept of partial inductances is used. The partial inductance technique appeared in the work by Rosa in the early 1900's [5]. Grover [6] provides a comprehensive tabulation of formulas for various geometries. Partial inductance method was formalized by Ruehli with the development of partial-element equivalent circuits (PEEC) [7-9]. The partial inductance technique can even be used to model the skin effect by dividing a conductor up into multiple longitudinal filaments [10-12]. However, in the partial inductance approach, the signal lines and supply and ground lines are treated equivalently, resulting in a large, densely coupled network representation.

We report our implementation of the Return-limited inductance method. The Return-limited inductance method obtains inductance matrix for the on-chip signal lines [13,14]. The inductances of the signal lines are extracted independently from the power and ground wires. Mutual inductances between signal lines are restricted by a set of geometry-based decomposition rules, which are referred to as halo rules. It is assumed that only Manhattan geometry is used, which means that all edges of all shapes are either horizontal or vertical to each other.

Section II describes Return-limited loop inductance method, Section III describes our implementation of RLI method, in Section IV we discuss numerical problems, the solution is provided in Section V and in Section VI we

<sup>1</sup> This work is supported by the Ministry of Science and Technology of the Republic of Croatia under the contract 0036027 "Semiconductor Device Modeling and High-Speed Circuit Design".

give results for various line structures, and Section VII contains the conclusion.

## II. RETURN-LIMITED INDUCTANCE METHOD

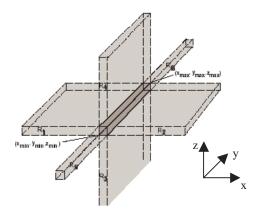

In orthogonal coordinate system horizontal refers to the x direction and vertical to the y direction. The z direction is perpendicular to the surface of the chip. A wire segment is a rectangular parallelepiped defined by coordinates ( $x_{min}$ ,  $y_{min}$ ,  $z_{min}$ ) and ( $x_{max}$ ,  $y_{max}$ ,  $z_{max}$ ). A horizontal segment is the one where the current flow is known to be horizontal and a vertical segment is the one where current flow is vertical, i.e. in the y direction.

The halo rules [13] are used to reduce signal line interactions:

- 1. Horizontal and vertical signal line segments are treated independently since they do not inductively couple to each other.

- 2. Horizontal halos of power and ground are "blocked" by horizontal signal segments, while vertical halos of power and ground are "blocked" by vertical segments.

- 3. Inductive coupling between two horizontal segments is nonzero if and only if it is possible to connect two segments by a path that does not cross horizontal halo of any ground or supply line. Similarly is for vertical segments.

Figure 1: The halo of a given segment consists of six semi-infinite regions.

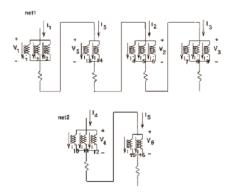

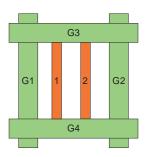

These halo rules divide the chip interconnect into a collection of horizontal and vertical interaction region (Fig. 1). After the interaction regions are defined, extraction begins by fracturing each wire into a set of segments. The model for each signal segment which results from fracturing is a resistance in series with a parallel

combination of (open) loop inductances, where each loop is defined by a signal line returning through one of the return segments defined on the parallel, adjacent supply or ground lines in the interaction region (Fig. 2). These inductances are called return-limited loop inductances. The matrix of return-limited loop inductances is transformed into the inductance matrix L for one interaction region by [13]

$$L = (B^{T} L^{-1} B)^{-1}$$

(1)

where L is the inductance matrix of the size  $m \times m$ , m is the number of signal segments in the interaction region, L' is the return-limited loop inductance matrix of the size  $n \times n$ , n is the number of return-limited loop inductances and B is the transformation matrix of the size  $n \times m$ , where the ith column of B is all zero except for the ones in rows corresponding to the return-limited loop inductances associated with the given signal segment inductance (return-limited inductance).

Figure 2. Signal line resistance and inductance representation for two

### III. IMPLEMENTATION OF THE RLI ALGORITHM

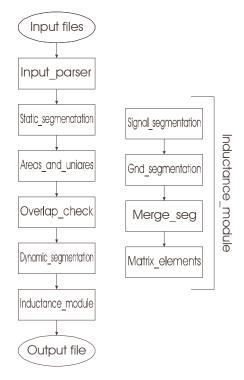

Inductance calculations based on the RLI method [13] are implemented. The code consists of a number of separate program modules that operate on geometric information stored in input files. Input files are used to describe layout of the chip and metal layers. Data flow diagram of the code is shown in Figure 3.

An input files are parsed through the **Input parser** module in order to obtain pure geometric information of the chip geometry. Main data needed for inductance calculations are geometry data of power, ground and signal lines. Static segmentation is performed next in order to obtain signal segments. It processes units of points and returns list of signal line segments defined by coordinates  $(x_{min}, y_{min}, z_{min})$  and  $(x_{max}, y_{max}, z_{max})$ . Depending on the power or ground line positions interaction regions are formed bases on halo rules [13], which is implemented in the module areas and uniareas. Dynamic segmentation of signal segments is done twice: 1. taking into account the geometry of the interaction regions (dynamic segmentation module), 2. taking into account segments positions (signal\_segmentation module). Beside

signal segmentations power or ground lines also have to be segmented. After both segmentations are done, all data is prepared for inductance calculations. Pure calculations are performed inside inductance module, which consists of few sub-modules that have specific tasks.

A brief description of important modules used in hierarchy of our code is given here:

- *input\_parser*: used for input of data that describe onchip geometry.

- *static\_segmentation*: processes units of points and returns list of signal line segments defined by coordinates  $(x_{min}, y_{min}, z_{min})$  and  $(x_{max}, y_{max}, z_{max})$ .

Figure 3. Data flow diagram.

- *areas\_and\_uniareas*: generates interaction region based on halo rules [13].

- overlap\_check: checks halo rules applied in areas\_and\_uniares module.

- dynamic\_segmentation: fractures signal line segments to fit inside interaction regions.

- *inductance\_module*: for each interaction region calculates inductance matrix.

### Sub-modules of **inductance module**:

- *signal\_segmentation*: fractures signal line segments inside interaction region.

- *gnd\_segmentation*: fractures power or ground lines.

- *merge\_seg*: searches inductance loops for signal segments through power or ground lines.

- *matrix\_elements*: calculates elements of return-limited loop inductance matrix.

There are also additional modules that are mainly used for data manipulations inside various data structures, errors reporting and similar maintenance tasks.

## IV. NUMERICAL PROBLEMS

After the implementation, several tests are performed. In the case that the signal segments have the same return loops, incorrect and nonphysical results are obtained, as it can be seen in (2)

$$L = \begin{bmatrix} 8.30259e - 011 & 1.13778e - 011 \\ 0 & 8.30259e - 011 \end{bmatrix}, H$$

(2)

Although there are no problems in the calculation of the return-limited loop inductance matrix L', the problems occur when transforming the return-limited loop inductance matrix L' into the inductance matrix L. The characteristics of the obtained return-limited loop inductance matrix L' are examined. The condition number is used to check the sensitivity of matrix when calculating the inverse matrix [15,16]. The condition number of the return-limited loop inductance matrices, obtained in such cases, has shown high sensitivity, e.g. the condition number of the L' is **92.5086** for the previous example, while the condition number for the lines that do not have the same return paths is close to 1, which means that inverse matrix can be accurately calculated.

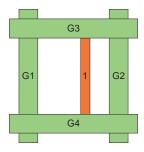

Figure 4. Signal lines with all current loops.

## V. SOLUTION

To solve the problem, a new rule is used: In cases in which two or more signal segments share exactly the same power or ground return loop, the return-limited loop inductance representation should contain only one loop (chosen arbitrarily) for the signals beyond the first [14]. In this case matrices have lower dimensions than before, except the final inductance matrix L, which is always of dimension  $m \times m$ , where m is number of signal line segments inside the interaction region.

Figure 5. Signal lines with reduced number of current loops.

The resulting matrix for two signal line segments from Figure 5. is given in (3). Its elements are self-inductance values ( $L_{11}$  and  $L_{22}$ ) and mutual inductance of segment 1 to segment 2 ( $L_{12}$ ) and vice versa ( $L_{21}$ )

$$L = \begin{bmatrix} 8.48049e - 011 & 1.57733e - 011 \\ 1.57733e - 011 & 7.92349e - 011 \end{bmatrix}, H$$

(3)

The condition number in this case is **8.60268**.

The results show that the self inductances are not equal, although they should be, because two equal signal line segments are used. The most probable cause for this inconsistency is exclusion of current return paths for one signal line segment. Note that the mutual inductances are equal, as expected.

If only one segment is calculated, the self inductance is equal to 85 pH, which is very close to  $L_{II}$ . When calculating the inductance matrix in (3), the second return path of the segment 2 has been neglected, which confirms the assumption for the cause of error in the calculation of self inductances.

## VI. ANALYSES FOR DIFFERENT CASES

Several examples and corresponding results will be presented here. The results are compared to the results obtained by FastHenry tool [11,12]. In these examples we study results only in one interaction region. In the very first example, the self-inductance values obtained by our program are compared to the values obtained by FastHenry.

Example 1: The self-inductances of a single line segment inside interaction region are calculated. Constant parameters are width of the segment (10 um) and thickness (1 um). Length of the segment is changed from 20 um to 1000 um.

Figure 6. Self-inductance.

Comparing results (Table 1) obtained by FastHenry and by our program we get to the conclusion that our results are very similar to ones obtained by FastHenry, but are slightly higher.

Table 1: Self-inductance comparison.

| length, um    | 20   | 50   | 100  | 200 | 500 | 1000 |

|---------------|------|------|------|-----|-----|------|

| FastHenry, pH | 7.31 | 27.7 | 68.6 | 164 | 501 | 1140 |

| this work, pH | 7.82 | 32.8 | 85   | 206 | 610 | 1320 |

Example 2: In this example mutual inductances of two line segments inside interaction region are compared. Constant parameters are: width of the segments (10 um), thickness (1 um) and length (100 um). We change distance between segments in the range from 10 um to 500 um.

Figure 7. Mutual inductance.

Table 2: Mutual inductance comparison.

| distance, um  | 10 | 20 | 50 | 100 | 200 | 500 |

|---------------|----|----|----|-----|-----|-----|

| FastHenry, pH | 31 | 23 | 14 | 9   | 5   | 3   |

| this work, pH | 47 | 40 | 31 | 25  | 20  | 16  |

From results given in Table 2. it is obvious that the values obtained by our code are higher than ones obtained by FastHenry, as it was with self-inductance values.

# VII. CONCLUSION

The implementation of the algorithm for on-chip inductance extraction based on the return-limited

inductance method is presented. The implementation of the RLI method is undertaken to see how close the results of the RLI method are to the results obtained by much more complicated and slower method, i.e. the FastHenry program. Also, the calculated inductances may be further used for the optimization of interconnects. The numerical problems with inverse matrix calculations are solved, but the accuracy of the results is violated. Finally, several structures are analyzed for various lengths, widths and distances between lines. The obtained results show that this implementation results in inductance values slightly higher than the inductances obtained by FastHenry, which is used as the reference method.

#### REFERENCES

- Yehea I. Ismail, "On-Chip Inductance Cons and Pros," *IEEE Transactions on VLSI Systems*, vol. 10, no. 6, pp. 685-694, Dec. 2002

- [2] G. V. Kopcsay, B. Krauter, D. Widiger, A. Deutsch, B. J. Rubin, and H. H. Smith, "A Comprehensive 2-D Inductance Modeling Approach for VLSI Interconnects: Frequency-Dependent Extraction and Compact Circuit Model Synthesis," *IEEE Transactions on VLSI Systems*, vol. 10, no. 6, pp. 695-711, Dec. 2002.

- [3] M. W. Beattie and L. T. Pileggi, "On-Chip Induction Modeling: Basics and Advanced Methods," *IEEE Transactions on VLSI Systems*, vol. 10, no. 6, pp. 712-729, Dec. 2002.

- [4] M. Liu, T. Yu, and W. W.-M. Dai, "Fast 3-D Inductance Extraction in Lossy Multi-Layer Substrate," *Proc. ICCAD* 2001, San Jose, pp. 424-429, Nov. 2001.

- [5] E. B. Rosa, "The self and mutual inductance of linear conductors," Bulletin of the National Bureau of Standards, vol. 4, pp. 301-344, 1908.

- [6] F. Grover, "Inductance Calculations: Working Formulas and Tables," New York: Dover, 1962.

- [7] A. E. Ruehli, "Inductance calculations in a complex integrated circuit environment," *IBM J. Res Develop.*, vol. 16, no. 5, pp. 470-481, 1972.

- [8] A. E. Ruehli, "Equivalent circuit models for three-dimensional multiconductor systems," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-22, pp. 216-221, Mar. 1974.

- [9] A. E. Ruehli, N. Kulasza, and J. Pivnichny, "Inductance of nonstraight conductors close to a ground return plane," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-22, pp. 706-708, Aug. 1975.

- [10] W. T. Weeks, L. L. Wu, M. F. McAllister, and A. Singh, "Resistive and inductive skin effects in rectangular conductors," *IBM J. Res. Develop.*, vol. 23, no. 6, pp. 652-660, 1979.

- [11] M. Kamon, M. J. Tsuk, and J. White, "FastHenry, a multipole-accelerated 3-D inductance extraction program," *Proc. 30th ACM/IEEE Design Automation Conf.*, Dallas, TX, pp. 678-683, June 1993.

- [12] M. Kamon, M. J. Tsuk, and J. White, "FASTHENRY: A multipole-accelerated 3-D inductance extraction program," *IEEE Trans. Microwave Theory and Tech.*, vol. 42, pp. 1750-1758, Sept. 1994.

- [13] K. L. Shepard and Z. Tian, "Return-limited inductance: A practical approach to on-chip inductance extraction," *IEEE Transactions on CAD*, vol. 19, no. 4, pp. 425-436, April 2000.

- [14] K. L. Shepard, D. Sitaram, and Yu Zheng, "Full-chip, three-dimensional, shapes-based RLC extraction," *Proceedings of the International Conference on Computer-Aided Design*, pp. 142-149, 2002

- [15] http://planetmath.org/encyclopedia/MatrixConditionNumber.html

- [16] http://www.cs.ut.ee/~toomas\_l/linalg/lin1/node18.html