# UNIVERSITY OF ZAGREB

# FACULTY OF ELECTRICAL ENGINEERING AND COMPUTING

MASTER'S THESIS no. 1031

# PARALLEL MACHINE SIMULATOR

Stjepan Antivo Ivica

Zagreb, June 2015.

#### SVEUČILIŠTE U ZAGREBU FAKULTET ELEKTROTEHNIKE I RAČUNARSTVA ODBOR ZA DIPLOMSKI RAD PROFILA

Zagreb, 26. veljače 2015.

Predmet:

Paralelno programiranje

# DIPLOMSKI ZADATAK br. 1031

Pristupnik: Studij: Profil: Stjepan Antivo Ivica (0036448356) Računarstvo Računarska znanost

## Zadatak: Simulator paralelnog računala sa zajedničkom memorijom

#### Opis zadatka:

Opisati problem simulacije rada sinkronog i asinkronog paralelnog računala sa zajedničkom memorijom. Istražiti postojeće postupke simulacije s obzirom na sintaksu nastalog jezika i dosljednost modelu. Ostvariti sustav koji simulira paralelno računalo sa zajedničkom memorijom. Ocijeniti korisnost simulatora s obzirom na postojeće probleme koji se rješavaju paralelnim računalom sa zajedničkom memorijom. Predložiti strukturu jezika i preporučene metode interpretacije jezika. Usporediti učinkovitost simulatora s postojećim simulatorima navedenog modela. Radu priložiti izvorne tekstove programa, dobivene rezultate uz potrebna objašnjenja i korištenu literaturu.

Zadatak uručen pristupniku: 13. ožujka 2015. Rok za predaju rada: 30. lipnja 2015.

Mentor: A1.80

Izv. prof. dr. sc. Domagoj Jakobović

Djelovođa:

Doc. dr. sc. Tomislav Hrkać

| Predsje   | dnik odbora za   |

|-----------|------------------|

| diploms   | ski rad profila: |

| $\supset$ | $\bigcirc$       |

Prof. dr. sc. Siniša Srbljić

#### UNIVERSITY OF ZAGREB FACULTY OF ELECTRICAL ENGINEERING AND COMPUTING MASTER THESIS COMMITTEE

Zagreb, 26 February 2015

#### MASTER THESIS ASSIGNMENT No. 1031

Student:Stjepan Antivo Ivica (0036448356)Study:ComputingProfile:Computer Science

Title: Parallel machine simulator

Description:

Describe the problem of simulation of synchronous and asynchronous parallel computer with shared memory. Examine existing simulation implementations with respect to the syntax of the language and consistency to the model. Implement a system that simulates a parallel computer with shared memory. Assess the usefulness of the simulator with regard to existing problems solved with a parallel computer with shared memory. Propose the structure of the language and the recommended methods of interpretation. Compare the effectiveness of the simulator with existing simulators of this model. Submit the original program code, results obtained with the necessary explanations and used literature.

Issue date: Submission date: 13 March 2015 30 June 2015

Mentor:

Associate Professor Domagoj Jakobović, PhD

Committee Secretary:

Committee Chair:

wo. In In

Full Professor Siniša Srbljić, PhD

Assistant Professor Tomislav Hrkać, PhD

# Sadržaj

| 1. Intr | oduction1                                             |  |  |  |  |  |  |  |

|---------|-------------------------------------------------------|--|--|--|--|--|--|--|

| 1.1.    | Random Access Machine (RAM) Model 1                   |  |  |  |  |  |  |  |

| 1.2.    | Abstract computer for designing parallel algorithms 2 |  |  |  |  |  |  |  |

| 2. PR   | AM programming model4                                 |  |  |  |  |  |  |  |

| 2.1.    | Handling shared memory access conflicts4              |  |  |  |  |  |  |  |

| 2.2.    | All – Prefix – Sums (Scan operation)5                 |  |  |  |  |  |  |  |

| 2.3.    | Implementation of parallel scan operation             |  |  |  |  |  |  |  |

| 2.4.    | Down – sweep 8                                        |  |  |  |  |  |  |  |

| 2.5.    | Complexity of the scan operation9                     |  |  |  |  |  |  |  |

| 3. Inte | erpreter                                              |  |  |  |  |  |  |  |

| 3.1.    | Interpreter Language 11                               |  |  |  |  |  |  |  |

| 3.2.    | Pre – interpreter statements 12                       |  |  |  |  |  |  |  |

| 3.3.    | Interpreter statements 14                             |  |  |  |  |  |  |  |

| 4. Arc  | hitecture                                             |  |  |  |  |  |  |  |

| 4.1.    | Spring Context Framework 18                           |  |  |  |  |  |  |  |

| 4.2.    | Maven                                                 |  |  |  |  |  |  |  |

| 4.3.    | Jython 19                                             |  |  |  |  |  |  |  |

| 4.4.    | Packages overview                                     |  |  |  |  |  |  |  |

| 4.4.1   | hr.fer.zemris.parallelmachinesimulator                |  |  |  |  |  |  |  |

| 4.4.2   | 2. Interpreter                                        |  |  |  |  |  |  |  |

| 4.4.3   | B. Pre interpreter 22                                 |  |  |  |  |  |  |  |

| 4.4.4   | 4. Output 23                                          |  |  |  |  |  |  |  |

| 4.4.5   | 5. Model 23                                           |  |  |  |  |  |  |  |

| 4.4.6   | 6. PRAM Processor                                     |  |  |  |  |  |  |  |

| 4.4.7   | I.7. Exception 2                                      |  |  |  |  |  |  |  |

|    | 4.4.8. Expres |              | Expression                  | 25 |  |  |  |

|----|---------------|--------------|-----------------------------|----|--|--|--|

|    | 4.4.          | 9.           | Memory                      | 26 |  |  |  |

| 5. | Exa           | ampl         | es and demos                | 27 |  |  |  |

| 5  | .1.           | Sca          | an and reduce               | 27 |  |  |  |

| 5  | .2.           | Sha          | ared memory model violation | 27 |  |  |  |

| 5  | .3.           | CRCW example |                             |    |  |  |  |

| 5  | .4.           | ER           | EW algorithm example        | 30 |  |  |  |

| 6. | Oth           | ner s        | olutions and comparison     | 32 |  |  |  |

| 6  | 5.1.          | For          | k                           | 32 |  |  |  |

| 7. | Co            | nclu         | sion                        | 33 |  |  |  |

| 8. | Lite          | eratu        | re                          | 34 |  |  |  |

| 9. | Su            | Summary      |                             |    |  |  |  |

# 1. Introduction

Parallel Machine Simulator (*PMS*) is an interpreter for execution of programs made for Parallel Random Access Machine (*PRAM*). PMS is intended for execution on Random Access Machine (RAM) for purposes of testing and emulation. Interpreter language created for interpreter has a Python – like syntax.

## 1.1. Random Access Machine (RAM) Model

Traditionally, software has been written for serial computation. A problem is broken into a discrete series of instructions. Instructions are executed sequentially one after another.

Random Access Machine (RAM) is a favorite model of a sequential computer. RAM model has unbounded number of local memory cells. Instruction set includes operations for moving data between memory cells, comparisons and conditional branches, and simple arithmetic operations. Execution of program starts with the first instruction and ends when a HALT instruction is executed. All operations take unit time regardless of the lengths of operands. Time complexity is equal to the number of instructions executed. Space complexity is equal to the number of memory cells accessed.

Under this model of computation, we are confronted with a computer where:

• Each simple operation (+, \*, -, =, if, call) takes exactly one time step.

• Loops and subroutines are not considered simple operations.

• Each memory access takes exactly one time step. Further, we have as much memory as we need. The RAM model takes no notice of whether an item is in cache or on the disk.

Under the RAM model, we measure run time by counting up the number of steps an algorithm takes on a given problem instance. If we assume that our RAM executes a given number of steps per second, this operation count converts naturally to the actual running time.

The RAM is a simple model of how computers perform. Perhaps it sounds too simple. After all, multiplying two numbers takes more time than adding two numbers on most processors, which violates the first assumption of the model. It strikes a fine balance by capturing the essential behavior of computers while being simple to work with. RAM model is useful in practice.

### 1.2. Abstract computer for designing parallel algorithms

PRAM is a straightforward and natural generalization of RAM. PRAM model has an unbounded collection of numbered RAM processors P0, P1, P2,... and an unbounded collection of shared memory cells M[0], M[1], M[2],.... Each Pi has its own (unbounded) local memory (registers) and knows its index i. Each processor can access any shared memory cell (unless there is an access conflict, see further) in unit time. Input at a PRAM algorithm consists of n items stored in (usually the first) n shared memory cells. Output of a PRAM algorithm consists of n' items stored in n' shared memory cells.

PRAM instructions execute in 3-phase cycles: 1) Read (if any) from a shared memory cell, 2) Local computation (if any) and 3) Write (if any) to a shared memory cell. Processors execute these 3-phase PRAM instructions synchronously. The only way processors can exchange data is by writing into and reading from memory cells.

Special assumptions have to be made about shared memory access conflicts. P0 has a special activation register specifying the maximum index of an active processor. Initially, only P0 is active, it computes the number of required active processors and loads this register, and then the other corresponding processors start executing their programs.

Computation proceeds until P0 halts, at which time all other active processors are halted. Parallel time complexity is equal to the time elapsed for P0's computation. Space complexity is equal the number of shared memory cells accessed.

PRAM is an attractive and important model for designers of parallel algorithms. It is natural: the number of operations executed per one cycle on p processors is at most p. It is strong: any processor can read or write any shared memory cell in unit time. It is simple: it abstracts from any communication or synchronization overhead, which makes the complexity and correctness analysis of PRAM algorithms easier. Therefore, it can be used as a benchmark: If a problem has no feasible/efficient solution on PRAM, it has no feasible/efficient solution on any parallel machine. It is useful: it is an idealization of existing (and nowadays more and more abundant) shared memory parallel machines.

The PRAM corresponds intuitively to the programmers' view of a parallel computer: it ignores lower level architectural constraints, and details, such as memory access contention and overhead, synchronization overhead, interconnection network throughput, connectivity, speed limits and link bandwidths, etc.

# 2. PRAM programming model

As its name indicates, the PRAM was intended as the parallel-computing analogy to the random-access machine (RAM). In the same way that the RAM is used by sequential-algorithm designers to model algorithmic performance (such as time complexity), the PRAM is used by parallel-algorithm designers to model parallel algorithmic performance (such as time complexity, where the number of processors assumed is typically also stated). Similar to the way in which the RAM model neglects practical issues, such as access time to cache memory versus main memory, the PRAM model neglects such issues as synchronization and communication, but provides any (problem-size-dependent) number of processors.

PRAM corresponds intuitively to the programmers' view of a parallel computer: it ignores lower level architectural constraints, and details, such as memory access contention and overhead, synchronization overhead, interconnection network throughput, connectivity, speed limits and link bandwidths, etc.

# 2.1. Handling shared memory access conflicts

To make the PRAM model realistic and useful, some mechanism has to be defined to resolve read and write access conflicts to the same shared memory cell.

Concurrent Read Concurrent Write (CRCW) PRAM: Both simultaneous reads and simultaneous writes of the same memory cell are allowed.

*Concurrent Read Exclusive Write* (CREW) PRAM: Simultaneous reads of the same memory cell are allowed, but only one processor may attempt to write to an individual cell.

*Exclusive Read Concurrent Write* (ERCW) PRAM: Simultaneous writes to the same memory cell are allowed, but only one processor may attempt to read from an individual cell.

*Exclusive Read Exclusive Write* (EREW) PRAM: No two processors are allowed to read or write the same shared memory cell simultaneously.

Assume p-processor PRAM, p<n. Assume that shared memory contains n distinct items and P0 owns value x. The task is to let P0 know whether x occurs within the input array.

EREW PRAM algorithm:

- 1) P0 broadcasts x to P1,...,Pp in log p steps using binary broadcast tree.

- 2) All processors perform local searches, each on [n/p] items in [n/p] steps.

- Every processor defines a flag Found and all processors perform a parallel reduction.

$T(n,p)=\log p + n/p$

ERCW PRAM algorithm: is rarely considered, due in part to a general belief that concurrent writing does not add much power to a model without concurrent reading. There are some algorithms that solve problems on the ERCW PRAM much faster than they could be solved on the EREW PRAM. Here the algorithm and the complexity would be the same as EREW.

CREW PRAM algorithm: A similar approach, but P1,...,Pp can read x simultaneously in O(1) time. But the final reduction takes O(log p) time anyway, so

$T(n,p)=\log p + n/p$

CRCW PRAM algorithm: The final step takes now also O(1) time, those processors with the flag Found set can write simultaneously into P0's cell

T(n,p)=n/p.

PMS interpreter is designed to test algorithms on these models. Breaking constraints of memory model in interpreter results with no execution of block and an error message.

## 2.2. All – Prefix – Sums (Scan operation)

Many of the blocks and tools needed for parallel algorithms extend from sequential algorithms, such as dynamic-programming and divide – and – conquer, but others are new. This chapter introduces one of the simplest and most useful building blocks for parallel algorithms: the all – prefix – sums operation. In addition to being a useful building block, the all – prefix – sums operation is a good example of a computation that seems inherently sequential, but for which there is an efficient parallel algorithm.

The operation is defined as follows: The all-prefix-sums operation takes a binary associative operator  $\oplus$ , and an ordered set of n elements  $[a_0, a_1, ..., a_{n-1}]$ , and returns the ordered set  $[a_0, (a_0 \oplus a_1), ..., (a_0 \oplus a_1 \oplus ... \oplus a_{n-1})]$ .

For example, if  $\oplus$  is addition, then the all-prefix-sums operation on the ordered set [3, 1, 7, 0, 4, 1, 6, 3], would return [3, 4, 11, 11, 14, 16, 22, 25].

The uses of the all-prefix-sums operation are extensive. Some of them are: To lexically compare strings of characters. For example, to determine that "strategy" should appear before "stratification" in a dictionary. To add multi precision numbers; these are numbers that cannot be represented in a single machine word. To evaluate polynomials. To solve recurrences; for example, to solve the recurrences  $x_i = a_i x_i - 1 + b_i x_i - 2$  and  $x_i = a_i + b_i / x_i - 1$ . It can be used to implement sorting algorithms such as radix sort and quicksort. Known uses extend to other problems such as solving tridiagonal linear systems, deletion marked elements from an array, dynamic allocation of processors and labeling components in two dimensional images. All – prefix – sums can be used to perform lexical analysis. For example, to parse a program into tokens, search for regular expressions or to implement the UNIX grep program. There are even uses for some tree operations like finding the depth of every vertex in a tree.

In fact, all – prefix – sums operations using addition, minimum and maximum are so useful in practice that they have been included as primitive instructions in some machines. Researchers have also suggested that a subclass of the all – prefix – sums operation be added to the PRAM model as a "unit time" primitive because of their efficient hardware implementation.

The algorithm require O(n) time. To execute the all – prefix – sums operation in parallel, the algorithms must be changed significantly.

### 2.3. Implementation of parallel scan operation

For p processors and a vector of length n on an EREW PRAM, the algorithm has a time complexity of  $O(n/p + \lg p)$ . The algorithm is simple and well suited for direct implementation in hardware. Scan operation with certain operators can be reduced to  $O(n/p + \lg p/ \lg \lg p)$  on a CREW PRAM.

Reduce operation is a simpler problem, that of generating only the final element of the scan. The reduce operation takes a binary associative operator  $\oplus$  with identity *I*, and an ordered set [a<sub>0</sub>, a<sub>1</sub>, ..., a<sub>n-1</sub>] of n elements, and returns the value (a<sub>0</sub>  $\oplus$  a<sub>1</sub>  $\oplus$  ...  $\oplus$  a<sub>n-1</sub>).

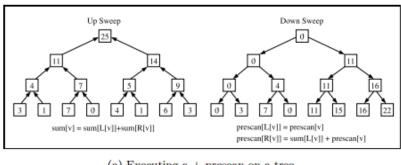

We consider only the case where the ordered set is kept in a vector. A balanced binary tree can be used to implement the reduce operation by laying the tree over the values, and using  $\oplus$  to sum pairs at each vertex. The correctness of the result relies on  $\oplus$  being associative. The operator does not need to be commutative since the order of the operands is maintained. On an EREW PRAM, each level of the tree can be executed in parallel, so the implementation can step from the leaves to the root of the tree; we call this an up – sweep. Since the tree is of depth [lg n], and one processor is needed for every pair of elements, the algorithm requires O(lg n) time and n/2 processors. If we assume a fixed number of processors p, with n > p, then each processor can sum an n/p section of the vector to generate a processor sum.

The time taken to generate the processor sums is [n/p], so the total time required on an EREW PRAM is:  $T_R(n, p) = [n/p] + [lg p] = O(n/p + lg p)$ . When n/p  $\geq$  lg p the complexity is O(n/p). This time is an optimal speedup over the sequential algorithm.

After the implementation of the prescan operation the scan operation is then determined by shifting the result and putting the sum at the end. If we look at the tree generated by the reduce operation, it contains many partial sums over regions of the vector. It turns out that these partial sums can be used to generate all the prefix sums. This requires executing another sweep of the tree with one step per level, but this time starting at the root and going to the leaves (a down – sweep). Initially, the identity element is inserted at the root of the tree. On each step, each vertex at the current level passes to its left child its own value, and it passes to its right child,  $\oplus$  applied to the value from the left child from the up – sweep and its own value. A parallel prescan on a tree using integer addition as the associative operator.

# 2.4. Down – sweep

After a complete down-sweep, each vertex of the tree contains the sum of all the leaf values that precede it. Vertex x precedes vertex y if x appears before y in the preorder traversal of the tree.

| procedure down-sweep(A) |                                                                               |                     |                  |             |                    |        |     |        |       |

|-------------------------|-------------------------------------------------------------------------------|---------------------|------------------|-------------|--------------------|--------|-----|--------|-------|

|                         | $a[n-1] \leftarrow 0$ % Set the identity<br>for d from $(\lg n) - 1$ downto 0 |                     |                  |             |                    |        |     |        |       |

|                         | in parallel for i from 0 to $n-1$ by $2^{d+1}$                                |                     |                  |             |                    |        |     |        |       |

|                         |                                                                               | $i + 2^{d} -$       |                  |             | 5 10 1             |        |     | n temp | orarv |

|                         |                                                                               | <sup>d</sup> − 1] ← |                  | $2^{d+1}$ - | - 11               |        |     | ft chi |       |

|                         | a[i + 2                                                                       | d+1 - 1             | $\leftarrow t +$ | a[i +       | 2 <sup>d+1</sup> - | 1] %   |     |        |       |

|                         |                                                                               |                     |                  |             |                    | 1      |     | -      |       |

|                         | Step                                                                          |                     |                  |             | Vector             | in Mem | ory |        |       |

|                         | 0                                                                             | [ 3                 | 1                | <b>7</b>    | 0                  | 4      | 1   | 6      | 3     |

| up                      | 1                                                                             | [ 3                 | 4                | 7           | 7                  | 4      | 5   | 6      | 9     |

| -                       | 2                                                                             | 3                   | 4                | 7           | 11                 | 4      |     | 6      | 14    |

|                         | 3                                                                             | [3                  | 4                | 7           | 11                 | 4      | 5   | 6      | 25    |

| clear                   | 4                                                                             | [3                  | 4                | 7           | 11                 | 4      | 5   | 6      | 0]    |

| down                    | 5                                                                             | [ 3                 | 4                | 7           | 0                  | 4      | 5   | 6      | 11]   |

|                         | 6                                                                             | [ 3                 | 0                | 7           | 4                  | 4      | 11  | 6      | 16    |

|                         | 7                                                                             | [ 0                 | 3                | 4           | 11                 | 11     | 15  | 16     | 22]   |

(a) Executing a +-prescan on a tree.

(b) Executing a +-prescan on a PRAM.

# Figure 1 A parallel prescan on a tree using integer addition as the associative operator

We must show that if a parent has the correct sum, both children must have the correct sum. The root has no elements preceding it, so its value is correctly the identity element. The left child of any vertex has exactly the same leaves preceding it as the vertex itself. This is because the preorder traversal always visits the left child of a vertex immediately after the vertex. Using induction, the parent has the correct sum, so it need only copy this sum to the left child. The right child of any vertex has two sets of leaves preceding it, the leaves preceding the

parent, and the leaves at or below the left child. By adding the parent's down – sweep value, which is correct by the induction hypothesis, and the left – child's up – sweep value, the right – child will contain the sum of all the leaves preceding it.

Leaf values that precede any leaf are the values to the left of it in the scan order, the values at the leaves are the results of a left – to – right prescan. To implement the prescan on an EREW PRAM, the partial sums at each vertex must be kept during the up-sweep so they can be used during the down – sweep. Each step can execute in parallel, so the running time is  $2[\lg n]$ .

# 2.5. Complexity of the scan operation

If we assume a fixed number of processors p, with n > p, we can use a similar method to that in the reduce operation to generate an optimal algorithm. Each processor first sums an n/p section of the vector to generate a processor sum, the tree technique is then used to prescan the processor sums. The results of the prescan of the processor sums are used as an offset for each processor to prescan within its n/p section.

The time complexity of the algorithm is:  $T_S(n, p) = 2([n/p] + [lg p]) = O(n/p + lg n)$ . Which is the same order as the reduce operation and is also an optimal speedup over the sequential version when  $n/p \ge lg p$ .

# 3. Interpreter

We wanted to create a tool that will interpret code written for PRAM computer and simulate its behavior. PMS is interpreter. Interpreter is a computer program that directly executes instructions written in a programming or scripting language, without previously compiling them into a machine language program.

Focus of the PMS is functionality not performance. Having this in mind and that Python is one of the most popular languages we have decided to adopt Python – like syntax for the PMS.

There were two possible approaches to build such a tool. First approach was to create entirely new language and interpreter for it. Second approach was to create pre – interpreter that would be on top of another component. We have decided for the second approach, pre – interpreter on top of the Python interpreter.

Python is a widely used general-purpose, high – level programming language. Its design philosophy emphasizes code readability, and its syntax allows programmers to express concepts in fewer lines of code than would be possible in languages such as C++ or Java. The language provides constructs intended to enable clear programs on both a small and large scale.

Python supports multiple programming paradigms, including object – oriented, imperative and functional programming or procedural styles. It features a dynamic type system and automatic memory management and has a large and comprehensive standard library.

Python interpreters are available for installation on many operating systems, allowing Python code execution on a wide variety of systems. Using third – party tools Python code can be packaged into stand – alone executable programs for some of the most popular operating systems, allowing for the distribution of Python – based software for use on those environments without requiring the installation of a Python interpreter.

CPython, the reference implementation of Python, is free and open – source software and has a community-based development model, as do nearly all of its alternative implementations. CPython is managed by the non – profit Python Software Foundation.

### 3.1. Interpreter Language

An interpreted language is a programming language for which most of its implementations execute instructions directly, without previously compiling a program into machine-language instructions. The interpreter executes the program directly, translating each statement into a sequence of one or more subroutines already compiled into machine code.

The terms *interpreted language* and *compiled language* are not well defined because, in theory, any programming language can be either interpreted or compiled. In modern programming language implementation it is increasingly popular for a platform to provide both options.

Interpreted languages can also be contrasted with *machine languages*. Functionally, both execution and interpretation mean the same thing — fetching the next instruction/statement from the program and executing it. The term "interpreted" is practically reserved for "software processed" languages (by virtual machine or emulator) on top of the native processor.

In principle, programs in many languages may be compiled or interpreted, emulated or executed natively, so this designation is applied solely based on common implementation practice, rather than representing an essential property of a language.

Avoiding compilation, interpreted programs are easier to evolve during both development and execution. On the other hand, since compilation implies translation into more machine – friendly format, interpreted programs run more slowly and less efficiently (waste considerably more energy). This is especially true for higher – level scripting languages, whose statements are complex to analyze compared to machine instruction.

As already mentioned PMS interpreter is inspired by existing Python interpreter. Syntax of PMS is intended to expand on the syntax of the Python 2.7 version. Minimum executable unit for interpreter is block.

Block is a section of code which is grouped together. Blocks consist of one or more declarations and statements. A programming language that permits the creation of blocks, including blocks nested within other blocks, is called a block –

structured programming language. Blocks are fundamental to structured programming, where control structures are formed from blocks.

The function of blocks in programming is to enable groups of statements to be treated as if they were one statement, and to narrow the lexical scope of variables, procedures and functions declared in a block so that they do not conflict with variables having the same name used elsewhere in a program for different purposes. In a block-structured programming language, the names of variables and other objects such as procedures which are declared in outer blocks are visible inside other inner blocks, unless they are shadowed by an object of the same name.

PMS follows Python interpreter behavior when interacting with users. Interpreter will prefix beginning of every user's line input with '... ' if there is a current block that is not finished, otherwise it will put '>>> '.

PMS forbids usage of tabs. This was done because mixing whitespace and tabs bring mess into the code and possibly can lead to unwanted outcomes. Using whitespace is strongly encouraged.

Statements interpreter understands are divided into pre – interpreter statements and interpreter statements. Interpreter statements are instructions to be executed on the interpreter. While pre – interpreter statements manipulate interpreter itself.

# 3.2. Pre – interpreter statements

Pre - interpreter statements and their short description can be found at Table 1 Pre – interpreter statements and short description.

| Statement | Short Description                               |

|-----------|-------------------------------------------------|

| Comment   | Comments in the code                            |

| Load      | Loads external source of code                   |

| PRAM      | Sets memory model (RAM, CRCW, CREW, ERCW, EREW) |

| Reset     | Resets PMS                                      |

| Verbose   | Sets additional information during              |

| execution |

|-----------|

#### Table 1 Pre – interpreter statements and short description

*Comment* is a programming language construct used to embed programmer – readable annotations in the source code of a computer program. Those annotations are potentially significant to programmers but are generally ignored by compilers and interpreters. Comments start with '#' and continue to the end of the line. Interpreter will disregard anything that is commented. Inputting a line that is commented at its beginning will start a block, this behavior was adopted from Python interpreter. Example of line that is commented at its beginning:

# This is a comment

Instead of making interpreter relying heavily on user's line by line manual input we have decided that a good option of input would be from the file. There are algorithms and procedures that are common, loading those common parts of the code may be useful. Also writing code in the file and loading it may also be very useful. *Load* statement will calculate its whitespace offset and when inserting loaded content it will prefix with the same whitespace offset as calculated. *Load* statement is used to input code to interpreter from the file. *Load* pre – interpreter statement form is:

:load <file> where file is relative or absolute path to the file that user wants to load from.

We have discussed how there are different memory models for making PRAM more real. *PRAM* pre – interpreter statement changes memory model of the interpreter. There are five memory models RAM, CRCW, CREW, ERCW and EREW. Memory model cannot be changed inside of the block, it must be standalone statement. Changing memory model does not change variables in the local namespace or any other state of the interpreter. Default memory model when PMS starts is RAM. Form of the *PRAM* pre – interpreter statement is:

:pram <MODEL> where MODEL is one of the five available memory models.

After each execution of block, variables that interpreter has stored will persist. Sometimes in between blocks it is useful to remove any changes done to the memory. *Reset* statement will reset the local namespace of the interpreter to the state it was when it started. *Reset* will clean all the memory locations that user has manipulated. *Reset* takes no arguments. Reset cannot be executed inside block, it must be a standalone command. Form of the reset pre – interpreter statement is:

#### :reset reset takes no arguments

During the execution some information is available regarding what is happening in the interpreter. In this current version PMS can inform the client about what are the memory locations that were accessed by corresponding nodes during the execution of code in parallel environment. Client can decide to be fully informed or not be informed at all with *Verbose* statement. *Verbose* command can be executed within a block if user desires. When PMS starts verbosity is set to false. Form of the verbose pre – statement is:

:verbose <Boolean> where Boolean can be replaced with Boolean value true or false. It is case insensitive.

#### 3.3. Interpreter statements

Depending on the memory model interpreter available statements are different. If the memory model is RAM all the statements that are in Python 2.7 interpreter will be able to translate. If the memory model is any of the PRAM models then only *Assignment, For, If, Parallel, Pass, Print* and *While* statements are available and no function can be called within parallel block. Statements and their short descriptions can be found at Table 2 Interpreter statements and short description for each.

Additionally, *scan* function is defined for all the models. If there is any error with any of the statements in the block such as syntax error or memory violation, PMS will return the state of the local variable namespace to the state before the execution of block that contains such an error.

Assignment statement is used for binding a value to a memory location with assignment operation. It is done with assignment operator '='. Assignment operation for PRAM model has additional constraint that it can contain only one assignment operator in that line. Assignment operation can be standalone

statement or it can be included in the block. It cannot start a block. Form of the *Assignment* statement is:

| Interpreter statement | Short description                         |  |  |  |

|-----------------------|-------------------------------------------|--|--|--|

| Assignment            | Assign value to memory location           |  |  |  |

| For                   | Loop for iteration over sequence          |  |  |  |

| lf                    | Branching statement                       |  |  |  |

| Parallel              | Loop for parallel iteration over sequence |  |  |  |

| Pass                  | Does nothing. Placeholder statement.      |  |  |  |

| Print                 | Printing values on standard output.       |  |  |  |

| While                 | Loop with iteration under condition.      |  |  |  |

#### Table 2 Interpreter statements and short description for each

For statement is used to represent for loop. For loops are traditionally used when you have a piece of code which you want to repeat n number of times. For statement iterates over the items of any sequence (a list or a string), in the order that they appear in the sequence. It can iterate over number generator or over generated numbers. For loop can be standalone statement or it can be included in the block. It must start a block. Form of the For statement is:

for <it> in <range>: where it is iterator variable that iterates over assigned

#statement(s) range

*If* statement is probably the most well-known statement type for flow control. There is no support for 'else' and 'elif' statements. *If* statement takes Boolean expression that we will name condition. If the condition is true, then do the indented statements. If the condition is not true, then skip the indented statements. *If* statement can be standalone statement or it can be included in the block. It must start a block. Form of the *If* statement:

if ( <condition> ): parenthesis is optional. Condition is Boolean expression.

#### #statement(s)

Parallel statement can be only executed if any of PRAM memory models is active (EREW, ERCW, CREW, CRCW). Parallel statement cannot be inside sub block of another Parallel statement. Parallel statement can be standalone statement or it can be included in the block. It must start a block. Parallel statement syntax resembles for loop statement syntax. Parallel statement distributes one variable, which we will call inherited node property variable, over desired number of nodes. Each inherited node property variable's value is determined by the value of element with the same intent in assignment list as the index of the node receiving the value. Values can be the same or different, it depends on the user's desires. Statement also declares that entire block of the Parallel statement will be instantly executed over desired number of nodes. Form of the parallel statement is:

Parallel <imp> in <al>: where imp is inherited property node variable

```

#statement(s) and al is assignment list

```

The *Pass* statement does nothing. It can be used when a statement is required syntactically but the program requires no action. *Pass* statement can be standalone statement or it can be included in the block. It can not a block. Form of the *Pass* statement is:

pass pass takes no arguments

*Print* evaluates one expression and writes resulting object to standard output. If an object is not a string, it is first converted to a string using the rules for string conversions. The (resulting or original) string is then written. *Print* statement can be standalone statement or it can be included in the block. It can not a block. Form of the *Print* statement is:

print <rhs> where rhs is right hand side expression

A *While* loop statement repeatedly executes a target statement as long as a given condition is true. There is no support for 'else' statement. *While* loop can be standalone statement or it can be included in the block. It must start a block. There is no support for 'else' statement. Form of the *While* statement is:

while (<conditional>): parenthesis is optional. Condition is Boolean expression.

#### #statement(s)

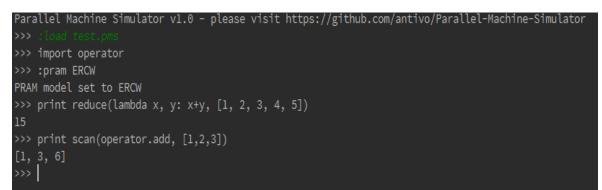

*Scan* function has signature scan(function, iterable[, state]), where function is the associative function, iterable is the iterable container and state is the value to be added to each element of the result. For example list(scan(operator.add, [1,2,3])) returns [1, 3, 6].

Reduce function has signature Reduce(function, iterable[, initializer]). Reduce function applies function of two arguments cumulatively to the items of iterable, from left to right, so as to reduce the iterable to a single value. For example, reduce(lambda x, y: x+y, [1, 2, 3, 4, 5]) calculates (((((1+2)+3)+4)+5)). The left argument, x, is the accumulated value and the right argument, y, is the update value from the iterable. If the optional initializer is present, it is placed before the items of the iterable in the calculation, and serves as a default when the iterable is empty. If initializer is not given and iterable contains only one item, the first item is returned.

# 4. Architecture

PMS is written as Java 8 project. Maven is used as build automation tool. It uses Spring Context framework for dependency injection and inversion of control. Jython interpreter is used as Python interpreter.

#### 4.1. Spring Context Framework

The Spring Framework is an application framework and inversion of control container for the Java platform. The framework's core features can be used by any Java application, but there are extensions for building web applications on top of the Java EE platform. Although the framework does not impose any specific programming model, it has become popular in the Java community as an alternative to, replacement for, or even addition to the Enterprise JavaBean (EJB) model. The Spring Framework is open source.

Central to the Spring Framework is its inversion of control (IoC) container, which provides a consistent means of configuring and managing Java objects using reflection. The container is responsible for managing object life cycles of specific objects: creating these objects, calling their initialization methods, and configuring these objects by wiring them together.

Objects created by the container are also called managed objects or beans. The container can be configured by loading XML files or detecting specific Java annotations on configuration classes. These data sources contain the bean definitions that provide the information required to create the beans.

Objects can be obtained by means of either dependency lookup or dependency injection. Dependency lookup is a pattern where a caller asks the container object for an object with a specific name or of a specific type. Dependency injection is a pattern where the container passes objects by name to other objects, via either constructors, properties, or factory methods. In many cases one need not use the container when using other parts of the Spring Framework, although using it will likely make an application easier to configure and customize. The Spring container provides a consistent mechanism to configure applications and integrates with almost all Java environments, from small-scale applications to large enterprise applications.

You do not create an object, but describe how they should be created, by defining it in the Spring configuration file. You do not call services and components, but tell which services and components must be called, by defining them in the Spring configuration files. This makes the code easy to maintain and easier to test through IoC.

#### 4.2. Maven

Maven is a build automation tool used primarily for Java projects. The word maven means 'accumulator of knowledge' in Yiddish. Maven addresses two aspects of building software: First, it describes how software is built, and second, it describes its dependencies. Contrary to preceding tools like Apache Ant, it uses conventions for the build procedure, and only exceptions need to be written down. An XML file describes the software project being built, its dependencies on other external modules and components, the build order, directories, and required plugins. It comes with pre-defined targets for performing certain well-defined tasks such as compilation of code and its packaging. Maven dynamically downloads Java libraries and Maven plug-ins from one or more repositories such as the Maven 2 Central Repository, and stores them in a local cache. This local cache of downloaded artifacts can also be updated with artifacts created by local projects. Public repositories can also be updated.

Maven is built using a plugin-based architecture that allows it to make use of any application controllable through standard input.

### 4.3. Jython

Jython is an implementation of the Python programming language designed to run on the Java platform. It is the successor of JPython. From version 2.2 on, Jython (including the standard library) is released under the Python Software Foundation License (v2). The current release is Jython 2.7.0. It was released on 2015-05-02 and is compatible with Python 2.7.

Jython programs can import and use any Java class. Except for some standard modules, Jython programs use Java classes instead of Python modules. Jython includes almost all of the modules in the standard Python programming language distribution, lacking only some of the modules implemented originally in C. Jython compiles to Java bytecode (intermediate language) either on demand or statically.

Jython is complementary to Java and is especially suited for the following tasks: embedded scripting (addition of Jython libraries to some system allows end users to write scripts), interactive experimentation (Jython provides an interactive interpreter), rapid application development (Python programs are typically 2-10X shorter than the equivalent Java program).

#### 4.4. Packages overview

Let's make overview of the most important packages that contain crucial classes and mechanics behind them.

#### 4.4.1. hr.fer.zemris.parallelmachinesimulator

Parallel machine simulator package contains classes Main and Parallel Machine Simulator. It also contains sub packages: constants, exception, expression, interpreter, memory, model, output, pram processor, pre interpreter and utils.

Main class provides for Spring framework context. From that context Parallel Machine Simulator class is requested.

When Parallel Machine Simulator is started, banner message is printed, trace back is invoked and infinite loop is started. In the infinite loop input from user is obtained. If the input contains tabs exception is raised. If input contains no tabs its execution is forwarded to the Active Interpreter. Parallel Machine Simulator takes responsibility for receiving input and not allowing exception to leave infinite loop.

#### 4.4.2. Interpreter

Interpreter package contains interfaces Interpreter and Python interpreter; and also classes Active Interpreter, Interpreter Factory Jython Interpreter and PRAM Interpreter. Interpreter interface has only one method named push that takes String and returns Boolean value. Method takes line to push into the interpreter and form a block. Return value of the function gives an answer if the pushed line has finished the block or not.

Python interpreter interface contains set of methods that are needed (expected) from a Python interpreter. As we have said PMS is designed to be on top of the Python interpreter. This interface makes a contract for desired functionalities.

Active Interpreter when called by Parallel Machine Simulator informs it if current block is completed or not so Parallel Machine Simulator can prompt user with corresponding start of line. Active Interpreter component takes lines of user input and forwards their execution to the Pre Interpreter, PRAM Interpreter or Python Interpreter. Pre Interpreter is first to be offered with line. If Pre Interpreter cannot process the line Active Interpreter will offer line to one of the interpreters. Until block is finished there can be no change of Interpreter. After block is finished reference to current Interpreter is removed. When there is no active block Active Interpreter will ask Interpreter Factory to provide him with an appropriate instance of Interpreter.

Interpreter Factory returns reference to the appropriate instance based on the current Active Memory Model. Both of the interpreters are singleton and factory just asks for the appropriate object from the Spring context.

Jython Interpreter implements Python interface. It is an adapter for the Interactive Console defined in the Jython library. This is the active interpreter if there is a line to be pushed and active memory model is RAM.

PRAM Interpreter is interpreter to be used when active memory model is not RAM. It organizes lines pushed to it into the blocks. Blocks are represented as graph of components that execute statements. Those components are named PRAM Processor (name may be misleading) objects. It decides upon indentation of lines to which block does that line belong to. It delegates creation of PRAM Processor objects to the PRAM Processor Factory. If the execution of block fails, PRAM Interpreter rolls back local variable state to the one previous to the execution of current block.

#### 4.4.3. Pre interpreter

Pre Interpreter package contains interface Pre Interpreter Directive and class Pre Interpreter. Within it package directive is contained. Package directive contains classes Comment, Load, PRAM, Reset and Verbose.

Pre Interpreter is hardcoded to take references to the classes Comment, Load, PRAM, Reset and Verbose when created. This is done because some pre – interpreter statements have higher precedence in front of others like Comment. More elegant solution can be made but for the current version of PMS we are satisfied with this solution. Upon offered with line Pre Interpreter will check if any of the Pre Interpreter Directives he has reference to can process given line in order. First Pre Interpreter Directive that can process is assigned for processing.

Pre Interpreter Directive is interface for declaring pre – interpreter statements. For every class that implements Pre Interpreter Directive it is important to define when it can process given line and how to process it.

Comment class implements Pre Interpreter Directive. It can process line if it contains character '#'. It removes commented part of the line and pushes the rest to the Parallel Machine Simulator.

Load class implements Pre Interpreter Directive. It takes responsibility for all the lines containing ':load' sequence. If in correct format it will read content of provided file and every line it has read will additionally prefix with the indentation that is equal to the indentation of load command itself. That content will be pushed to the Parallel Machine Simulator.

Reset class implements Pre Interpreter Directive. It can process all lines that are equal to the sequence ':reset' if there is no active interpreter at the moment (meaning there is no block being interpreted). Reset will delegate request to Parallel Machine Simulator. Parallel Machine Simulator will proceed with the resetting.

Verbose class implements Pre Interpreter Directive. It takes responsibility for all the lines containing ':verbose' sequence. If in correct format it will set Verbose Component to be verbose or not to be.

#### 4.4.4. Output

Package output contains only one class named Verbose Component. Verbose Component is designed to be entry point for all the output of the Parallel Machine Simulator. It is not fully developed. It should take responsibility for different levels of information and taking orders on which information should be printed on the output for the user.

#### 4.4.5. Model

Model package contains enum Memory Model and class Active Memory Model. Enum Memory Model enumerates memory models RAM, EREW, ERCW, CREW and CRCW and has static method for creating memory model object from String.

Active Memory Model class is singleton that is intended to contain information about current memory model. Every class that has to be have access this information has reference to this object.

#### 4.4.6. PRAM Processor

PRAM Processor package contains annotation PRAM Processor Statement, enum Block Property, interface PRAM Processor, abstract class PRAM Processor, class PRAM Processor Factory and package statement. Statement package contains classes Assignment, For, If, Parallel, Pass, Print and While.

PRAM Processor Statement has runtime retention and has method keyword that returns String. Its purpose is to mark statements that PRAM Interpreter can interpret.

Block Property is enumerator that enumerates CREATOR and BODY. These enumerations are used to mark PRAM Processors property for being able to create block or not to create block.

PRAM Processor is interface that defines that classes implementing it should have Memory Model, Body Property and indentation information. Public methods for assigning a line of interpreter language to it, pushing some other PRAM Processor to its sub block and execute method to execute assigned line and all the sub block that are pushed to it.

Abstract PRAM Processor defines common behavior for all the PRAM Processors. Abstract PRAM Processor defines how all the blocks define their

memory model from their parent's memory model and their default memory model. Each Abstract PRAM Processor defines its default memory model. Abstract PRAM Processor defines behavior for pushing itself to its parent Abstract PRAM Processor depending on indentation. It takes care that it is not able to receive any Abstract PRAM Processor as its child if it does not have appropriate Block Property. It also takes care of reporting it's ignore location, left hand side expression and right hand expression to the Expression receiver.

PRAM Processor Factory is assigned to create PRAM Processor based on the line that is supposed to assign, parent to which that line belongs and indentation (which is passed just for faster calculations). When created it acquires list of all the classes with PRAM Processor Statement annotation. When requested to create an instance of PRAM Processor it select from the catalogue it had acquired based on the keyword of that can be found in that line.

Assignment class extends Abstract PRAM Processor and is annotated with PRAM Processor statement. When requested Block Property it will return BODY. Its keyword is '='. Its lhs is equal to expression on the left of the equation operator and its rhs is equal to the expression on the right side of the equation operator. If the current memory model is not RAM and variable to which is being assigned does not already belong to the list it is added to the ignore list. Default memory model of assignment statement is RAM.

For class extends Abstract PRAM Processor and is annotated with PRAM Processor statement. When requested Block Property it will return CREATOR. Its keyword is 'for'. Its rhs is equal to the sequence being iterated over. It updates the list of ignored memory locations with variable that is iterating trough sequence if its memory model is not RAM. This is done because those for loops are being executed on every node and that variable is disjoint for all the nodes. Default memory model of for statement is RAM.

If class extends Abstract PRAM Processor and is annotated with PRAM Processor statement. When requested Block Property it will return CREATOR. Its keyword is 'if'. Its rhs is equal to the condition being examined. Default memory model of if statement is RAM.

Parallel class extends Abstract PRAM Processor and is annotated with PRAM Processor statement. When requested Block Property it will return CREATOR. Its keyword is 'parallel'. Its rhs is equal to the sequence being iterated over. Variable that is being divided among processors is added to the ignore list for every node. Default memory model of Assignment statement is equal to the current memory model of the Active Memory Model. Parallel interacts with Joint Memory and Expression Receiver to coordinate simulation of execution on nodes.

Pass class extends Abstract PRAM Processor and is annotated with PRAM Processor statement. When requested Block Property it will return BODY. Its keyword is 'pass'. Pass statement does not interact with any memory locations. Default memory model of pass statement is RAM. Execution of pass statement does not change anything.

Print class extends Abstract PRAM Processor and is annotated with PRAM Processor statement. When requested Block Property it will return CREATOR. Its keyword is 'print'. . Its rhs is equal to the expression being printed. Default memory model of print statement is RAM.

While class extends Abstract PRAM Processor and is annotated with PRAM Processor statement. When requested Block Property it will return CREATOR. Its keyword is 'while'. Its rhs is equal to the condition being examined. Default memory model of while statement is RAM.

#### 4.4.7. Exception

Exception package contains classes Syntax Exception and Memory Violation. Both classes provide static factory methods for some standard occasions when they are raised. These two exceptions are the main exceptions that occur in the system. Syntax exception represents user's mistakes and Memory violation represents violation of the shared memory constraint.

#### 4.4.8. Expression

Expression package contains class Expression Receiver. This singleton class is the main point for all the expressions that PRAM Processors have to report. Expression that need to be reported are the left side expressions, right side expressions and expressions depicting variable locations that should be ignored by shared memory constraints. After being notified by Parallel, Expression Receiver will create Memory objects from all the locations and forward them to the Joint Memory.

#### 4.4.9. Memory

Memory package has three classes Joint Memory, Memory and Memory Factory.

Joint Memory class represents shared memory of the PRAM model. It takes responsibility to store all memory access per one node and for all nodes. If there has been violation of current active memory model Joint Memory will raise an exception.

Memory class represents memory location being use. Each Memory object is instructed how to check if it is equal location to another memory object. Two memory objects are considered equal if they both represent same memory location or if one memory object represents memory location that is subset of memory location that is represented by that other object. When two objects are determined to be the same transformation can be done. Transformation is when one of the objects is changed (the one that points to the smaller memory location) to contain the same data as the other object.

Memory Factory class creates Memory objects. Memory objects are created from appropriate String object.

# 5. Examples and demos

# 5.1. Scan and reduce

Example of executing scan and reduce function can be seen on Figure 2 Scan and reduce example. We can also see that PMS will greet user and direct him to check out web page where source code of PMS can be found. In this example we see that importing module works since we are in memory model RAM. User is using load statement to load code from file *'test.pms'*. On the picture user's input is in green. PMS output is in white. PRAM model is changed to ERCW. In the next line we have print statement that requires reduction over list of numbers with addition operator. In the line after that we can see scan function over list of natural numbers with addition operator.

#### Figure 2 Scan and reduce example

# 5.2. Shared memory model violation

In the Figure 3 Shared memory violation we can observe shared memory violation report from PMS. User's input is colored green, PMS output is colored white and PMS errors are colored red. User requested reset of the variables in the local namespace. Verbosity is set to true which means user will receive additional info that is available during execution. Memory model is set to ERCW. In the next few lines we have initialization of one dimensional arrays x and g and also initialization of two dimensional array y. Statement that follows is parallel statement. In the parallel statement it is defined that there will be three nodes each assigned with different value of variable *i*. In the other lines contained in that block we have assignments and reading from various memory locations. During the execution of second node memory violation has occurred. As we can see in this

example node with value i = 1 is reading from the memory location x[4], the same memory location that node with the value i = 2 is reading from.

```

Parallel Machine Simulator v1.0 - please visit https://github.com/antivo/Parallel-Machine

>>> :/ood Colt.px;

>>> :reset

Local namespace - reset

>>> :verbose true

Verbosity set to: true

>>> :pram ERCW

PRAM model set to ERCW

>>> x = [1,2,3,3,3,3,3]

>>> y = [[1,2,3],[1,2,3],[1,2,3],[1,2,3]]

>>> g = [1,2,3,4,5,6,7]

>>> parallel i in [1,2,3];

... j = i

... z = x[i -1] + 5 + y[x[j-1]][1]

... print z

... g[x[4] - 1] = 2

... print g[x[4] - 1]

... print 1

... print [1,2,3]

...

I [1, 2, 3]

-------RL: y[1][1], x[0], i, j, z, x[4], g[2]

-------Node with i = 2

9

Joint memory reading constraint violation. Multiple reading from memory locations: x[4]

>>>

```

#### Figure 3 Shared memory violation

# 5.3. CRCW example

In the Figure 4 CRCW algorithm we can observe the same problem with major difference, model is set to CRCW. In this model no shared model violation should occur. In the Figure 5 CRCW algorithm execution we can see the results of this algorithm on a CRCW model, due to verbosity command that has informed PMS to show additional information that is available. Output from the processors is divided by information of which values were assigned to nodes, from which locations those nodes were reading and to which location were writing as well as memory locations that would be ignored due to being associated to that node.

```

Parallel Machine Simulator v1.0 - please visit https://github.com/antivo/Parallel-Machine-Simulator

>>> :load test.

>>> :reset

Local namespace - reset

>>> import operator

>>> :verbose true

Verbosity set to: true

>>> :pram CRCW

PRAM model set to CRCW

>>> print reduce(lambda x, y: x+y, [1, 2, 3, 4, 5])

15

>>> print scan(operator.add, [1,2,3])

[1, 3, 6]

>>> y = [[1,2,3],[1,2,3],[1,2,3],[1,2,3]]

>>> g = [1,2,3,4,5,6,7]

>>> parallel i in [1,2,3]:

... z = x[i -1] + 5 + y[x[j-1]][1]

... print g[x[4] - 1]

```

#### Figure 5 CRCW algorithm execution

# 5.4. EREW algorithm example

Let's write an EREW algorithm that answers the question is the given array sorted in ascending order. If for each two adjacent elements in the input array left element is lesser than the right element of the pair we can say that array is sorted in ascending order.

Each PRAM processor can take care of one such pair and compare them. Because each node is making comparison between two nodes of the original array we will make a new array that is copy of original array. With this approach we will not violate any shared memory constrains. The result of comparisons we will store in separate array. If the total number of comparisons where left element was lesser than the right was equal to the number of total comparisons array is sorted in ascending order, otherwise it is not.

In Figure 6 EREW algorithm for determining if array is sorted in ascending order is presented this algorithm written for Parallel Machine Simulator. Code that can be seen in Figure 6 EREW algorithm for determining if array is sorted in ascending order written for Parallel Machine Simulatorstarts with statements that reset local namespace and decides not to take additional information that is available to the user during execution. When importing modules memory model must be changed to RAM because include statement can not be interpreted in any of the PRAM models in this current version of PMS. After all the preparations have been made it is usual to set desired memory model. In this case it is EREW. In this example we have hardcoded array of 10 elements sorted in ascending order from 0 to 9. Using the parallel loop we are creating copy of input array and initializing container for results of comparisons in constant time. Again using parallel block we are doing comparisons in constant time. When comparisons are done all that is left is using reduce function to count all the correctly ordered pairs. If that number is equal to the n-1 (because there are n-1 comparisons) we say the array is sorted, otherwise we say it is not.

```

:reset

:verbose false

:pram RAM

import random

import operator

:pram EREW

n = 10

p = [0, 1, 2, 3, 4, 5, 6, 7, 8, 9]

:pram EREW

copy = [0] * n #~copy = [0] * n

rez = [0] * n

parallel i in xrange(n):

rez[i] = 0

copy[i] = p[i]

parallel i in xrange(n-1):

if(copy[i] <= p[i+1]):

rez[i] = 1

# if sorted all nodes have done rez[i]=1, there were n-1 comparisons

uk = reduce(operator.add, rez);

isSorted = uk == (n-1)

if(isSorted):

print "SORTED!!"

if(not isSorted):

print "NOT SORTED!!"

```

Figure 6 EREW algorithm for determining if array is sorted in ascending order written for Parallel Machine Simulator

# 6. Other solutions and comparison

We haven't found any open source interpreters or compilers such that interpret or compile code intended for PRAM. But there is a language made for PRAM machines to which we will compare PMS.

# 6.1. Fork

Although criticized for being unrealistic, a PRAM has actually been realized in hardware in the 1990s by the SB-PRAM project of Wolfgang Paul's group at the University of Saarbrücken. Drawing upon hardware design techniques such as massive multithreading with cycle-by-cycle interleaving and a pipelined, combining interconnection network between processors and memory modules, it is a physical realization of a Combining Concurrent Read, Concurrent Write PRAM, and the strongest PRAM model known in theory. The largest operational SB-PRAM prototype (finished 2001) has 2048 (virtual) processors (corresponding to 64 processor boards). The architecture is scalable.

Fork is a programming language for the PRAM model; it has been implemented for the SB-PRAM.

Fork is based on ANSI C with extensions for the management of shared and private address subspaces and variables, and for static and dynamic nesting parallelism by processor group splitting constructs. The groups establish the scope of sharing and of synchronous execution. Fork offers full expressibility for many known parallel algorithmic paradigms like data parallelism, semaphorecoordinated asynchronous processes, pipelining and systolic algorithms, parallel task queue, and multiprefix, parallel divide-and-conquer, and even message passing.

Fork is lower lever language than PMS. PMS should be able to execute equivalent algorithms to those of Fork. PMS can be used as a high level language for writing proof of concept before writing the code in Fork. PMS to Fork is like Python to C with addition that PMS can be executed on RAM while fork is made for SB – PRAM.

# 7. Conclusion

The PRAM (Parallel Random Access Machine) is a multiprocessor. It is Synchronous MIMD with a consistent, sequential, shared memory that is accessible in unit time. Data locality, memory consistency and communication cost are completely abstracted and focuses on pure parallelism instead. Because of its simplicity, it is a very popular model of parallel computation in the theory of parallel algorithms.

Nowadays monolithic processor architectures are hitting the limits of their performance spectrum. Leakage currents, heat dissipation and energy consumption problems put another limit on the maximum clock frequency. Therefore multithreaded chip multiprocessors are becoming more and more mainstream architecture. In order to obtain speed-up on such an architecture, applications must be parallelized - not only at the instruction level, but also at loop and task level, which is a complex and time-consuming task with today's parallel supercomputers. Hence, a simple parallel programming model (and the PRAM is the simplest one) could be a realistic option for a future general – purpose programming model.

This trend is supported by developments in computer architecture, such as simultaneous multithreading, thread-level speculation, optical interconnects and network – on – chip technology.

We believe that PMS will prove to be useful tool in designing algorithms for PRAM. Currently there are no similar open source solutions that we have encountered.

# 8. Literature

- Jakobovic, Domagoj: "Predavanja iz kolegija Paralelno Programiranje", 2015

- 2. Blelloch, Guy: "Prefix Sums and Their Applications", School of Computer Science, Carnegie Mellon University, Pittsburgh

- 3. Skiena, Steven: "The Algorithm Design Manual (2nd ed.)", Springer Science+Business Media, 2010

- Tvrdik, Pavel: "PRAM model", <u>http://pages.cs.wisc.edu/~tvrdik/2/html/Section2.html</u>, 1999

- 5. "Python Tutorial", http://www.tutorialspoint.com/python/

- Juneau, Josh; Baker, Jim; Ng, Victor; Soto, Leo; Wierzbicki, Frank: "The Definitive Guide to Jython", <u>http://www.jython.org/jythonbook/en/1.0/index.html</u>, 2010

- "The Python Language Reference", <u>https://docs.python.org/2/reference/</u>, 2015

- Keller, Jörg; Kessler, Christoph W.; Träff, Jesper L.: "Practical PRAM Programming", <u>http://www.ida.liu.se/~chrke55/ppp.html</u>, 2001

- 9. "Parallel random-access machine", <u>http://en.wikipedia.org/wiki/Parallel\_random-access\_machine</u>, 2015

- 10. "Random-access machine", <u>http://en.wikipedia.org/wiki/Random-access\_machine</u>, 2014

- 11. "Interpreter (computing)", <u>http://en.wikipedia.org/wiki/Interpreter\_%28computing%29</u>, 2105

- 12. "Interpreted language", <u>http://en.wikipedia.org/wiki/Interpreted\_language</u>, 2015

- 13. "Block (programming)", <u>http://en.wikipedia.org/wiki/Block\_%28programming%29</u>, 2015

- 14. "Apache Maven", http://en.wikipedia.org/wiki/Apache\_Maven, 2015

- 15. "Python (programming language)", <u>http://en.wikipedia.org/wiki/Python\_%28programming\_language%29</u>, 2015

- 16. "Spring Framework", http://en.wikipedia.org/wiki/Spring\_Framework, 2015

# 9. Summary

Parallel Machine Simulator (*PMS*) is interpreter for execution of programs made for Parallel Random Access Machine (*PRAM*). PMS is intended for execution on Random Access Machine (RAM) for purpouses of testing and emulation. Interpreter language created for interpreter has Python – like syntax. PMS supports 5 different pre interpreter commands that can be used to manipulate PMS itself. Those statementss are *Comment, Load, PRAM, Reset* and *Verbose*. In RAM memory model PMS can interpret all Python statements. In any of the PRAM memory models (CRCW, CREW, ERCW and EREW) seven statements are available. Those statements are Assignment, For, If, Parallel, *Pass, Print* and *While*. Functions scan and reduce are also at disposal, those functions behavior is defined as it is expected from PRAM machine.

Keywords: Interpreter, PRAM, Python – like syntax

Parallel Machine Simulator (PMS) je interpreter namijenjen izvrsavanju programa namijenjenih na Parallel Random Access Machine (PRAM) računalima. PMS je alat koji se moze koristiti na Random Access Machine (RAM) računalima za potrebe testiranja i simulacije. Stvoreni jezik interpretera ima sintaksu sličnu Pythonu. PMS podržava 5 različitih pred interpreter naredbi kojima je moguće manipulirati sa PMS. Te naredbe su *Comment, Load, PRAM, Reset* and *Verbose*. U RAM memorijskom modelu PMS može interpretirati sve Python naredbe. U bilokojem od PRAM memorijskih modela (CRCW, CREW, ERCW i EREW) sedam naredbi je na raspolaganju. Te naredbe su *Assignment, For, If, Parallel, Pass, Print* and *While*. Postoje dodatne funkcije scan i reduce koje su na raspolaganju, a njihovo ponašanje je definirano kao i kod PRAM računala.

Keywords: Interpreter, PRAM, Python sintaksa